सानुकूलित पीसीबी असेंब्ली आणि पीसीबीए

वर्णन

| मॉडेल क्र. | ETP-005 | अट | नवीन |

| उत्पादन प्रकार | पीसीबी असेंब्ली आणि पीसीबीए | Min.Hole आकार | 0.12 मिमी |

| सोल्डर मास्क रंग | हिरवा, निळा, पांढरा, काळा, पिवळा, लाल इ पृष्ठभाग समाप्त | पृष्ठभाग समाप्त | HASL, Enig, OSP, गोल्ड फिंगर |

| किमान ट्रेस रुंदी/जागा | ०.०७५/०.०७५ मिमी | तांब्याची जाडी | 1 - 12 औंस |

| असेंब्ली मोड | एसएमटी, डीआयपी, छिद्रातून | अर्ज फील्ड | LED, वैद्यकीय, औद्योगिक, नियंत्रण मंडळ |

आमच्या पीसीबी बोर्ड डिझाइनबद्दल

जेव्हा आम्ही पीसीबी बोर्ड डिझाइन करतो, तेव्हा आमच्याकडे नियमांचा संच देखील असतो: प्रथम, सिग्नल प्रक्रियेनुसार मुख्य घटक स्थानांची मांडणी करा, आणि नंतर “सर्किट प्रथम कठीण आणि नंतर सोपे, घटक व्हॉल्यूम मोठ्या ते लहान, मजबूत सिग्नल आणि कमकुवत सिग्नल पृथक्करण, उच्च आणि निम्न.वेगळे सिग्नल, वेगळे अॅनालॉग आणि डिजिटल सिग्नल्स, वायरिंग शक्य तितक्या लहान करण्याचा प्रयत्न करा आणि लेआउट शक्य तितक्या वाजवी करा”;"सिग्नल ग्राउंड" आणि "पॉवर ग्राउंड" वेगळे करण्यासाठी विशेष लक्ष दिले पाहिजे;हे प्रामुख्याने पॉवर ग्राउंडला प्रतिबंध करण्यासाठी आहे.जर हा प्रवाह सिग्नल टर्मिनलमध्ये आणला गेला तर, तो चिपद्वारे आउटपुट टर्मिनलवर परावर्तित होईल, त्यामुळे स्विचिंग पॉवर सप्लायच्या व्होल्टेज नियमन कार्यक्षमतेवर परिणाम होईल.

त्यानंतर, घटकांची व्यवस्था स्थिती आणि वायरिंगची दिशा सर्किट डायग्रामच्या वायरिंगशी शक्य तितकी सुसंगत असावी, जी नंतरच्या देखभाल आणि तपासणीसाठी अधिक सोयीस्कर असेल.

ग्राउंड वायर शक्य तितकी लहान आणि रुंद असावी आणि पर्यायी प्रवाहातून जाणारी मुद्रित वायर देखील शक्य तितकी रुंद करावी.साधारणपणे, वायरिंग करताना आमचे एक तत्व असते, ग्राउंड वायर सर्वात रुंद असते, पॉवर वायर दुसरी असते आणि सिग्नल वायर सर्वात अरुंद असते.

फीडबॅक लूप, इनपुट आणि आउटपुट रेक्टिफिकेशन फिल्टर लूप एरिया शक्य तितक्या कमी करा, स्विचिंग पॉवर सप्लायमधील आवाज हस्तक्षेप कमी करणे हा हा उद्देश आहे.

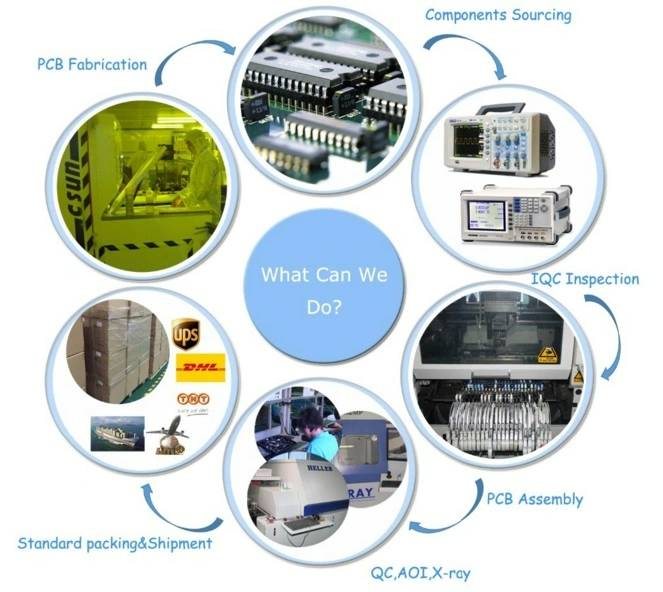

वन-स्टॉप सोल्यूशन

थर्मिस्टर सारखी प्रेरक उपकरणे उष्णतेच्या स्त्रोतांपासून किंवा हस्तक्षेपास कारणीभूत सर्किट उपकरणांपासून शक्य तितक्या दूर ठेवावीत.

ड्युअल इन-लाइन चिप्समधील परस्पर अंतर 2 मिमी पेक्षा जास्त असावे आणि चिप प्रतिरोधक आणि चिप कॅपेसिटरमधील अंतर 0.7 मिमी पेक्षा जास्त असावे.

इनपुट फिल्टर कॅपेसिटर फिल्टर करणे आवश्यक असलेल्या ओळीच्या शक्य तितक्या जवळ ठेवले पाहिजे.

PCB बोर्ड डिझाइनमध्ये, सर्वात सामान्य समस्या म्हणजे सुरक्षा नियम, EMC आणि हस्तक्षेप.या समस्यांचे निराकरण करण्यासाठी, डिझाइन करताना आपण तीन घटकांकडे लक्ष दिले पाहिजे: अंतराळ अंतर, क्रिपेज अंतर आणि इन्सुलेशन प्रवेश अंतर.प्रभाव.

उदाहरणार्थ: क्रीपेज अंतर: जेव्हा इनपुट व्होल्टेज 50V-250V असते, तेव्हा फ्यूजच्या समोरचा LN ≥2.5mm असतो, जेव्हा इनपुट व्होल्टेज 250V-500V असतो, तेव्हा फ्यूजच्या समोरचा LN ≥5.0mm असतो;इलेक्ट्रिकल क्लीयरन्स: जेव्हा इनपुट व्होल्टेज 50V-250V असते, फ्यूजच्या समोर L—N ≥ 1.7mm, इनपुट व्होल्टेज 250V-500V असते तेव्हा, L—N ≥ 3.0mm फ्यूजसमोर असते;फ्यूज नंतर कोणतीही आवश्यकता नाही, परंतु वीज पुरवठ्यामध्ये शॉर्ट सर्किटचे नुकसान टाळण्यासाठी विशिष्ट अंतर ठेवण्याचा प्रयत्न करा;प्राथमिक बाजू AC ते DC भाग ≥ 2.0 मिमी;प्राथमिक बाजू DC ग्राउंड ते ग्राउंड ≥4.0mm, जसे की प्राथमिक बाजू ते जमिनीवर;प्राथमिक बाजू ते दुय्यम बाजू ≥6.4 मिमी, जसे की ऑप्टोकपलर, वाय कॅपेसिटर आणि इतर घटक भाग, पिन अंतर 6.4 मिमी पेक्षा कमी किंवा समान आहे;ट्रान्सफॉर्मर टू-स्टेज ≥6.4 मिमी किंवा अधिक, प्रबलित इन्सुलेशनसाठी ≥8 मिमी.

फॅक्टरी शो

FAQ

Q1: तुम्ही PCBs ची गुणवत्ता कशी सुनिश्चित करता?

A1: आमचे PCB फ्लाइंग प्रोब टेस्ट, ई-टेस्ट किंवा AOI यासह सर्व 100% चाचणी आहेत.

Q2: लीड टाइम काय आहे?

A2: नमुन्यासाठी 2-4 कार्य दिवस आवश्यक आहेत, मोठ्या प्रमाणात उत्पादनासाठी 7-10 कार्य दिवस आवश्यक आहेत.हे फाइल्स आणि प्रमाणावर अवलंबून असते.

Q3: मला सर्वोत्तम किंमत मिळू शकते का?

A3: होय.ग्राहकांना किंमत नियंत्रित करण्यात मदत करण्यासाठी आम्ही नेहमीच प्रयत्न करत असतो.आमचे अभियंते पीसीबी सामग्री जतन करण्यासाठी सर्वोत्तम डिझाइन प्रदान करतील.